我p都不会还要考,天天考,考个甚么东西

第1章 开关理论基础

1.1 二进制系统

1.1.2 开关量

-

二进制系统:用电平的高和低表示物体的两种互斥状态,高电平表示1,低电平表示0

-

二进制系统的1和0是一个开关量,称为比特,两种状态的组合称之为码。

-

逻辑电平:用来表示数字0和1的电平称为逻辑电平,用来描述开关量。

1.2 数制与码制

1.2.1 进位计数制

- 二进制数的表示

1.2.2 进位计数制的相互转换

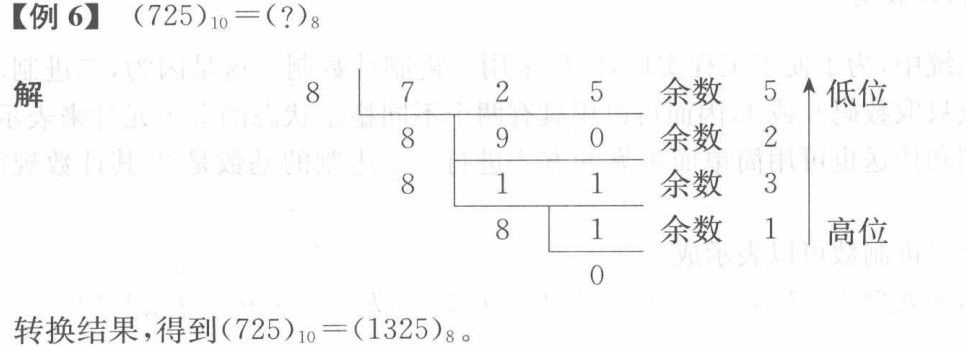

- 十进制整数转k进制:对k取余,结果由低位到高位排序

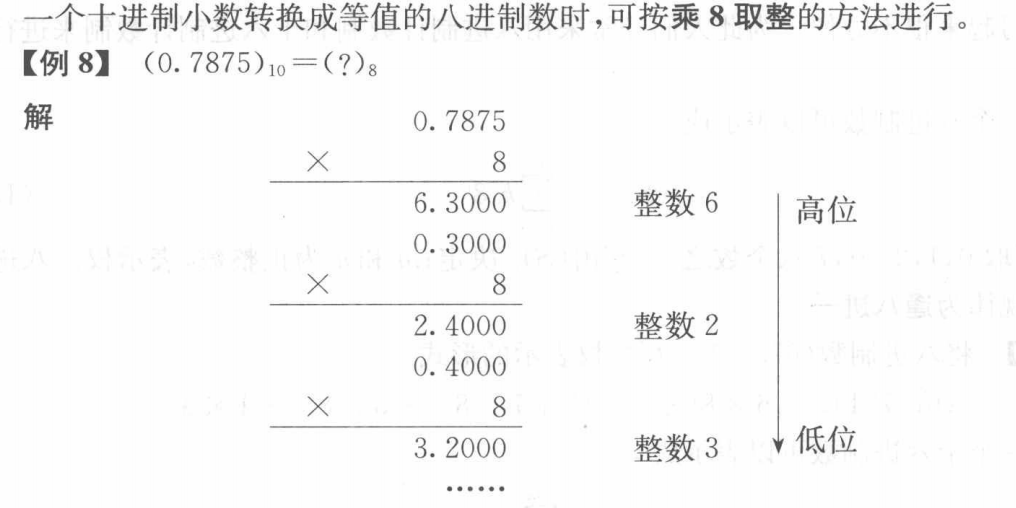

- 十进制小数转k进制:小数部分乘k,结果位由高到低排序

-

k进制转十进制:按位乘权值再求和

-

二八十六进制的相互转换:非常有趣,但懒得说了,dddd

1.2.3 二进制编码

-

自然二进制码是有权码,权值为

-

循环码无权,任意两个相邻码字中仅一位不同

-

BCD码(2-10进制码):每四位二进制码是一位十进制码,BCD码不能出现1010~1111这六个二进制数

- 8421码:编码值于0~9的ascii码低四位一致

- 5421码:最高位连续5个0后连续5个1,计数器采用这种码时最高位可形成对称方波输出(但我并不知道这有什么用)

- 2421码:是对9的补码

- 余3码:8421码的基础上每个码+0011,十进制相加时能正确产生进位信号

- 格雷码:循环码的一种

1.3 逻辑函数及其描述工具

1.3.1 逻辑函数的基本概念

- 逻辑函数:,其中F是输出,A是输入

1.3.2 逻辑函数的描述工具

-

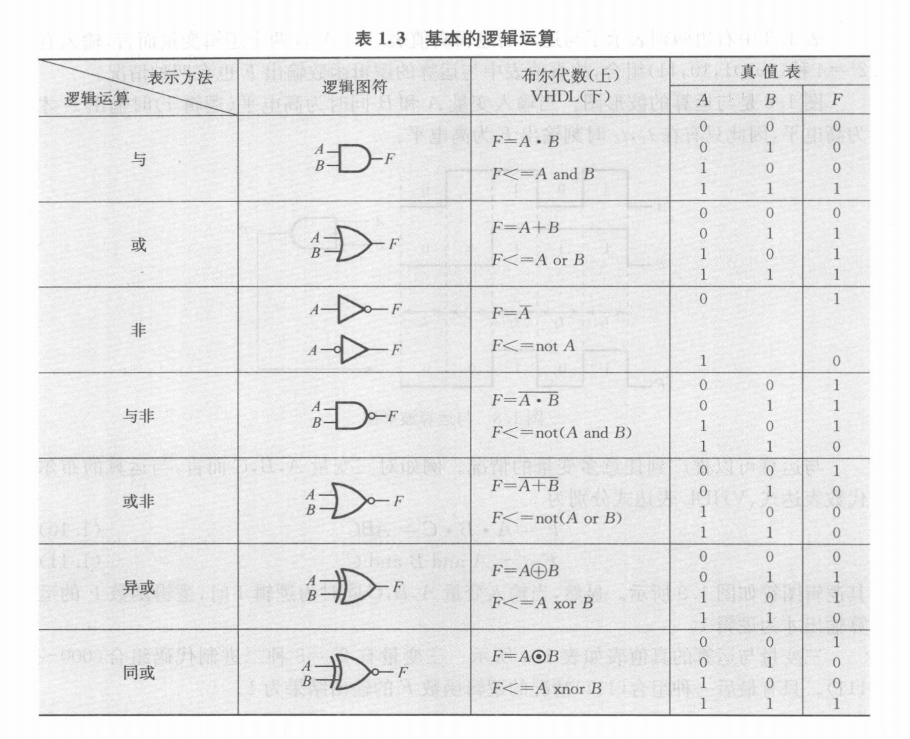

布尔代数:按逻辑规律进行运算的代数。

-

真值表:

狗都不看 -

逻辑图法:标准图形组成的表示逻辑函数运算关系的网络图形,瞎**画

-

卡诺图:是卡诺图捏

-

波形图:一上一下

1.3.3 基本逻辑运算

1.3.4 三态门

- 三态门:输出呈现逻辑1、逻辑0、高阻抗三种状态。使能端有效时输出状态取决于输入状态,使能端无效时输出端高阻态。

1.4 布尔代数

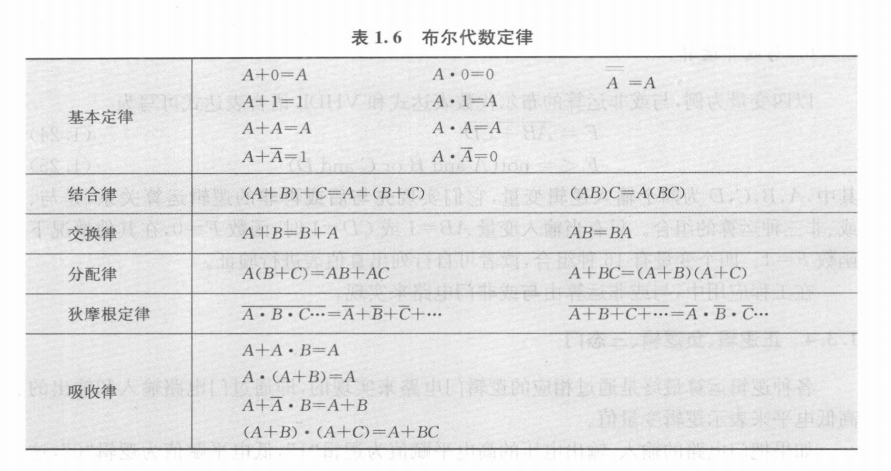

1.4.1 布尔代数的基本定律

1.4.2 布尔代数运算的基本规则

-

代入规则:在等式中所有出现A的位置都换成一个逻辑函数则等式仍然成立。

-

反演规则:将逻辑函数中的所有与或互换,是非变量互换,即可得到逻辑函数F的非函数

-

对偶规则:将F中的与或互换得到F'与F都成立

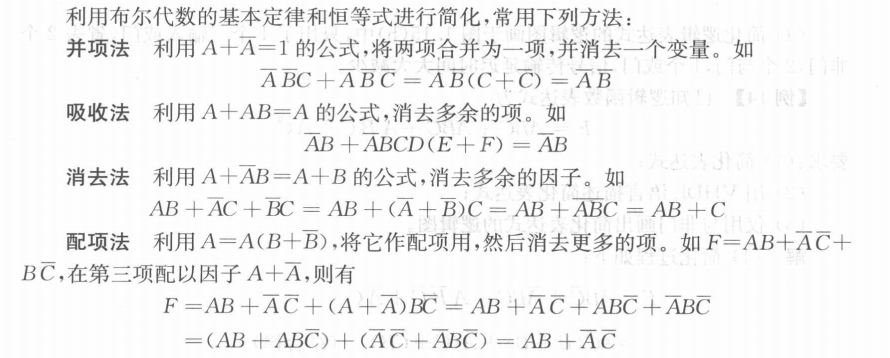

1.4.3 简化逻辑函数

- 最简与或表达式:乘积项数目最少且乘积项最少且每个乘积项中的变量个数也最少。

1.5 卡诺图

1.5.1 卡诺图结构

-

最小项表达式:最小项之和表示的逻辑函数

-

卡诺图:将最小项填入相应的特定方格图,任何一堆相邻最小项可以组合为比原最小项本身少一个变量的单项,几何相邻(对角也算)的两个最小项也是逻辑相邻的。

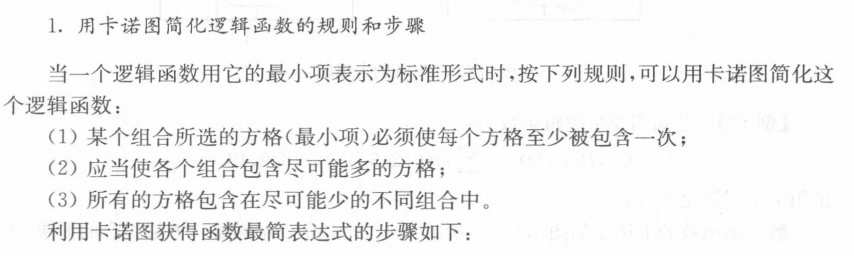

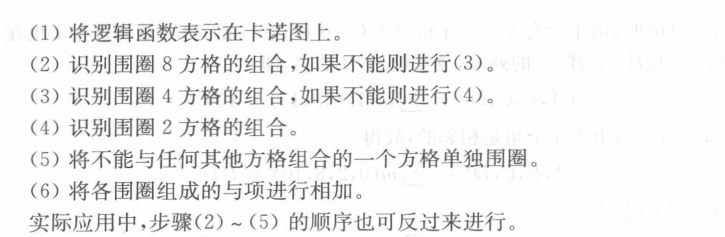

1.5.2 用卡诺图简化逻辑函数

第2章 组合逻辑

无反馈的逻辑电路称为组合逻辑电路。

2.1 组合逻辑分析

任意时刻的输出状态取决于该时刻信号的输入状态,而与信号作用前电路的状态无关。

组合逻辑电路分析的一般过程:阅读组合逻辑电路图->列写布尔表达式、真值表、画出数字波形图->指出电路的逻辑功能。

2.2 组合逻辑设计

2.2.1 组合逻辑设计步骤

- 将设计问题转化为逻辑问题或算法问题

- 将逻辑函数简化为最简与-或表达式

- 按形式画出逻辑图

2.3 组合逻辑电路的等价变换

2.3.1 德摩根定律的应用

或非门等价于非与门

2.4 数据选择器与分配器

2.4.1 数据选择器

- 数据选择器:多路输入、单路输出,输出取决于控制信号

74LS153

控制信号段S1,S0实现了对数据的选择,故常将其称为多路选择器的地址输入端

2.4.2 数据分配器

- 数据分配器:单路输入、多路输出的逻辑构件,选择输出的路径

2.5 译码器和编码器

2.5.1 译码器

74LS48 七段译码显示器

输入BCD码在对应的线路输出

2.5.2 编码器

判断输入信号并输出BCD码

-

普通编码器

-

优先编码器

普通编码器对输入先是有限制的,即同一时刻所有输入线中只允许一个一条有信号,不然就会混乱,但优先编码器对所有信号有效,并按预先设置的顺序排队

74LS148

2.6 数据比较器和加法器

2.6.1 数据比较器

74HC85 先高位后低位

2.6.2 加法器

-

串行加法器

-

并行加法器

74LS283

2.7 奇偶校验器

2.7.1 奇偶校验的原理

在码中附加一个校验位使得1的个数总是奇数或偶数

第3章 时序逻辑

输出往往反馈到输入端,和输入变量一起决定电路的输出状态,且任意时刻的输出不仅取决于该时刻输入变量的状态,而且还与原来的状态有关,因此时序电路具有记忆功能

3.1 锁存器

3.1.1 锁存器的基本特征

-

特性:

- 有两个互补的输出端

- 有两个稳定状态

- 在输入信号作用下,锁存器可以从一个稳定状态转换到零一个稳定状态

-

次态方程(特征方程):

其中X是输入信号的合集

3.1.2 基本SR锁存器

SR锁存器状态方程

3.1.3 门控SR锁存器

3.1.4 门控D锁存器

3.2 触发器

为提高锁存器工作的可靠性,推出了沿边沿触发的触发器

时钟端C外面不带小圆圈,表示时钟信号为正脉冲,带小圆圈则为负脉冲

3.2.1 SR触发器

3.2.2 D触发器

3.2.3 JK触发器

J和K都为1时改为交换Q的真值,改良了SR触发器

3.2.4 触发器的应用

-

用作并行数据存储器:一个触发器存一位二进制数,n个触发器并行连接,简称寄存器

-

用作计数器:n个触发器沿串行方式连接成n位计数器,可记忆2^n个状态

-

…(感觉剩下几种不太用记,不写了)

3.3 寄存器和移位寄存器

3.3.1 寄存器

- 寄存器:由触发器和锁存器构成,一次并行存储n位二进制数据的逻辑部件

74LS373

3.3.2 移位寄存器

- 移位寄存器:在时钟信号控制下,将所积存的数据向左或向右移位的寄存器

74LS299

3.4 计数器

计数器的功能是记忆脉冲的个数,它是数字系统中应用最广泛的基本时序逻辑构建,计数器所能记忆脉冲的最大数目称为模,用M表示,核心元件是触发器

-

分类:

- 计数功能:加法、减法、可逆

- 进位基数:二进制、十进制、任意进制

- 进位方式:同步(并行)、异步(串行)

3.4.1 同步计数器

3.4.2 异步计数器

异步计数器的时钟不来自同一个时钟源

3.4.3 中规模集成计数器及其应用

常选用达到最大模值的状态为终止状态

同步预置:加计数 预置值=N-M 减计数 预置值=M-1

异步预置:加计数 预置值=N-M-1 减计数 预置值=M

3.6 同步时序逻辑分析

3.6.1 同步时序逻辑电路的描述工具

-

米里型时序电路:输出不仅与该时刻的输入有关,而且与电路现态有关

-

摩尔型时序电路:输出只是状态变量的函数,与输入无关,或根本没有是食醋胡

状态表有两种形式:若用字母表示则称为状态表,若用二进制代码表示则称为状态转移表

3.6.2 同步时序电路的一般分析方法

- 给定逻辑图,写出输出函数和激励函数表达式

- 建立次态表达式及状态转移表

- 建立状态表及状态图

- 分析关系,说明功能

状态转移表(次态真值表)

第6章 数字系统

6.1 数字系统的基本概念

-

数字系统的定义:多个逻辑部件构成的具有存储、传输、处理信息能力的数字设备。包括存储部件、处理部件、控制部件等逻辑子系统。

-

数字系统是存储、传输、处理逻辑子系统的集合物。必须包含控制部件。

-

数字系统基本模型:输入、输出、逻辑系统(存储、处理、控制部件)

-

执行部件:根据控制信号进行数据运算、存储及传输。处理中产生状态信息反馈到控制部件。

-

控制部件:根据外部输入和状态反馈信息,向执行部件发送操作指令,决定何时、何地、何种数据运算。

-

控制单元是数字系统的重要标志和系统核心。

-

输入、输出部件: 输入部件接收外部信息,处理结果由输出部件供给外部环境。

-

逻辑系统:包括存储部件、处理部件、控制部件三大子系统。逻辑系统处理信息,

-

存储部件和处理部件在控制部件作用下工作,又称为执行(或受控)部件。

基本子系统

- 基本子系统是数字系统最基本的逻辑功能部件。包括算术逻辑单元ALU、寄存器堆、 RAM、数据通路和控制器。

6.2 数据通路

-

数据总线:数字系统中各子系统之间传送信息的公共通道称为数据总线。

-

数据通路:数字系统中各子系统之间通过数据总线连接形成的数据传送路径,称为数据通路。

-

分类:数据总线可分为控制总线、数据总线和地址总线。

6.3 自顶向下的设计方法

6.4 小型控制器的设计

未完待续 更新日期:2021/12/02